Ingenieria

Subcategoría

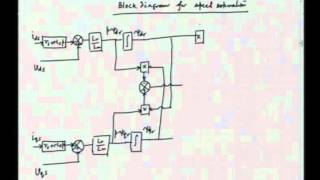

Power System Dynamics and Control by Dr. A.M. Kulkarni,Department of Electrical Engineering,IIT Bombay.For more details on NPTEL visit http://nptel.ac.in

Power System Dynamics and Control by Dr. A.M. Kulkarni,Department of Electrical Engineering,IIT Bombay.For more details on NPTEL visit http://nptel.ac.in

Power System Dynamics and Control by Dr. A.M. Kulkarni,Department of Electrical Engineering,IIT Bombay.For more details on NPTEL visit http://nptel.ac.in

Power System Dynamics and Control by Dr. A.M. Kulkarni,Department of Electrical Engineering,IIT Bombay.For more details on NPTEL visit http://nptel.ac.in

Power System Dynamics and Control by Dr. A.M. Kulkarni,Department of Electrical Engineering,IIT Bombay.For more details on NPTEL visit http://nptel.ac.in

Power System Dynamics and Control by Dr. A.M. Kulkarni,Department of Electrical Engineering,IIT Bombay.For more details on NPTEL visit http://nptel.ac.in

Power System Dynamics and Control by Dr. A.M. Kulkarni,Department of Electrical Engineering,IIT Bombay.For more details on NPTEL visit http://nptel.ac.in

Power System Dynamics and Control by Dr. A.M. Kulkarni,Department of Electrical Engineering,IIT Bombay.For more details on NPTEL visit http://nptel.ac.in

Power System Dynamics and Control by Dr. A.M. Kulkarni,Department of Electrical Engineering,IIT Bombay.For more details on NPTEL visit http://nptel.ac.in

Power System Dynamics and Control by Dr. A.M. Kulkarni,Department of Electrical Engineering,IIT Bombay.For more details on NPTEL visit http://nptel.ac.in

Power System Dynamics and Control by Dr. A.M. Kulkarni,Department of Electrical Engineering,IIT Bombay.For more details on NPTEL visit http://nptel.ac.in

Power System Dynamics and Control by Dr. A.M. Kulkarni,Department of Electrical Engineering,IIT Bombay.For more details on NPTEL visit http://nptel.ac.in

Power System Dynamics and Control by Dr. A.M. Kulkarni,Department of Electrical Engineering,IIT Bombay.For more details on NPTEL visit http://nptel.ac.in

Power System Dynamics and Control by Dr. A.M. Kulkarni,Department of Electrical Engineering,IIT Bombay.For more details on NPTEL visit http://nptel.ac.in

Power System Dynamics and Control by Dr. A.M. Kulkarni,Department of Electrical Engineering,IIT Bombay.For more details on NPTEL visit http://nptel.ac.in

Power System Dynamics and Control by Dr. A.M. Kulkarni,Department of Electrical Engineering,IIT Bombay.For more details on NPTEL visit http://nptel.ac.in

Power System Dynamics and Control by Dr. A.M. Kulkarni,Department of Electrical Engineering,IIT Bombay.For more details on NPTEL visit http://nptel.ac.in

Power System Dynamics and Control by Dr. A.M. Kulkarni,Department of Electrical Engineering,IIT Bombay.For more details on NPTEL visit http://nptel.ac.in

Power System Dynamics and Control by Dr. A.M. Kulkarni,Department of Electrical Engineering,IIT Bombay.For more details on NPTEL visit http://nptel.ac.in

Power System Dynamics and Control by Dr. A.M. Kulkarni,Department of Electrical Engineering,IIT Bombay.For more details on NPTEL visit http://nptel.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Intelligent Systems Control_M_3_L_6

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur.

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

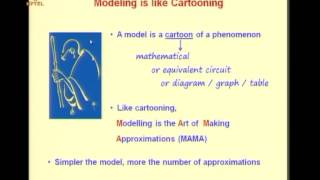

Intelligent Systems Control(M_1_L_3)Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof. Laxmidhar Behera, Department of Electrical Engineering, Indian Institute of Technology, Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Power System Operations and Control

Module_2

Lecture_5Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

Lectures by Prof.S.N.Singh Department of Electrical Engineering IIT Kanpur. For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

High Voltage DC Transmission by Prof.S.N.Singh,Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

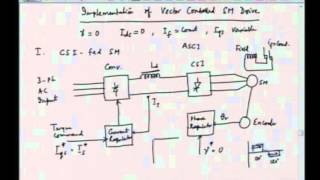

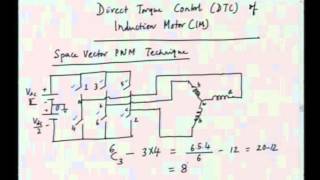

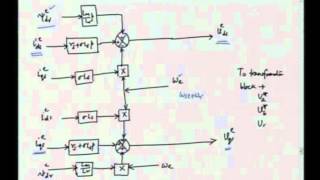

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

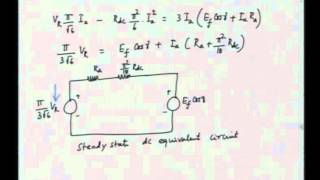

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

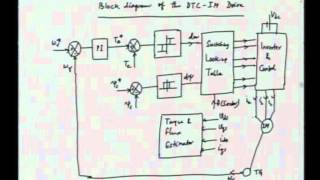

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

Advanced Electric Drives by Dr. S.P. Das, Department of Electrical Engineering,IIT Kanpur.For more details on NPTEL visit http://nptel.iitm.ac.in

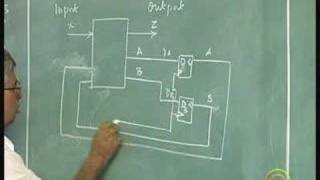

Lecture Series on Computer Organization by Prof.S. Raman, Department of Computer Science and Engineering, IIT Madras. For More details on NPTEL visit http://nptel.iitm.ac.in

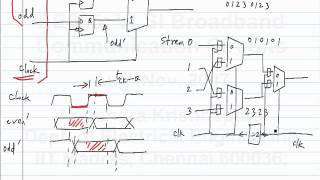

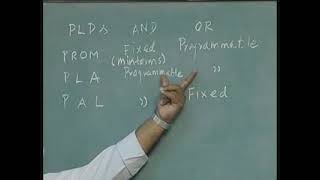

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Digital Circuit system

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof.S.Srinivasan, Department of Electrical Engineering, IIT Madras.For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof. S. Srinivasan,

Department of Electrical Engineering, IIT Madras

For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture series on Digital Circuits & Systems by Prof.S.Srinivasan, Department of Electrical Engineering, IIT Madras.For more details on NPTEL visit http://nptel.ac.in

Lecture Series on Electronics for Analog Signal Processing I by Prof. K. Radhakrishna Rao, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics for Analog Signal Processing I by Prof. K. Radhakrishna Rao, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics for Analog Signal Processing I by Prof. K. Radhakrishna Rao, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics for Analog Signal Processing I by Prof. K. Radhakrishna Rao, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics for Analog Signal Processing I by Prof. K. Radhakrishna Rao, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics for Analog Signal Processing I by Prof. K. Radhakrishna Rao, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics for Analog Signal Processing I by Prof. K. Radhakrishna Rao, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics for Analog Signal Processing I by Prof. K. Radhakrishna Rao, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing I by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Electronics For Analog Signal Processing part-II by Prof.K.Radhakrishna Rao, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

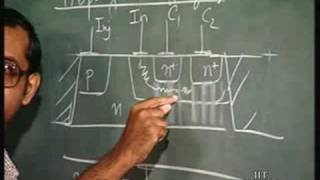

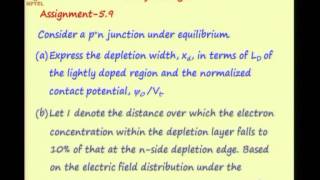

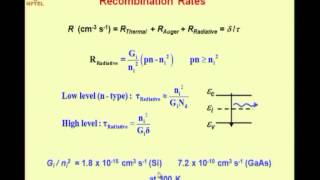

Solid State Devises

Solid State Devices

Solid State Devices

Solid State Devices

Solid State Devices

Solid State Devices

Solid State Devices

Solid State Devices

Solid State Devices

Solid State Devices

Solid State Devices

Solid State Devices

Solid State Devices

Solid State Devices

Solid State Devices

Solid State Devices

Solid State Devices

Solid State Devices

Solid State Devices

Solid State Devices

Solid State Devices

Solid State Devices

Solid State Devices

Solid State Devices

Solid State Devices

Solid State Devices

Solid State Devices

Solid State Devices

Lecture series on Solid State Devices by Prof S.Karmalkar, Dept of Electrical Engineering IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Solid State Devices

Lecture Series on Solid State Devices by Dr.S.Karmalkar, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Solid State Devices by Dr.S.Karmalkar, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Solid State Devices by Dr.S.Karmalkar, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Solid State Devices by Dr.S.Karmalkar, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Solid State Devices by Dr.S.Karmalkar, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Solid State Devices by Dr.S.Karmalkar, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Solid State Devices by Dr.S.Karmalkar, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Solid State Devices by Dr.S.Karmalkar, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Solid State Devices by Dr.S.Karmalkar, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Solid State Devices by Dr.S.Karmalkar, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Solid State Devices by Dr.S.Karmalkar, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Solid State Devices by Dr.S.Karmalkar, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

VLSI

VLSI

VLSI

VLSI

VLSI

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on VLSI Design by Dr.Nandita Dasgupta, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.ac.in

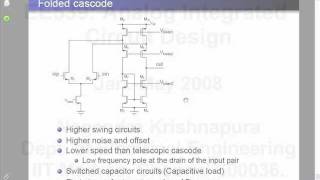

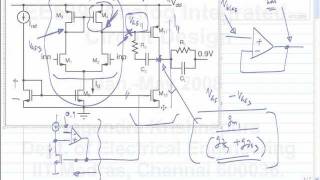

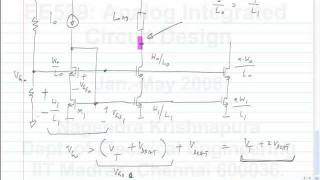

Lecture Series on Analog ICs by Prof. K. Radhakrishna Rao, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K. Radhakrishna Rao, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K. Radhakrishna Rao, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K. Radhakrishna Rao, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K. Radhakrishna Rao, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K. Radhakrishna Rao, Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K.Radhakrishna Rao , Department of Electrical Engineering,I.I.T.Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K.Radhakrishna Rao , Department of Electrical Engineering,I.I.T.Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K.Radhakrishna Rao , Department of Electrical Engineering,I.I.T.Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K.Radhakrishna Rao , Department of Electrical Engineering,I.I.T.Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K.Radhakrishna Rao , Department of Electrical Engineering,I.I.T.Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K.Radhakrishna Rao , Department of Electrical Engineering,I.I.T.Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K.Radhakrishna Rao , Department of Electrical Engineering,I.I.T.Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K.Radhakrishna Rao , Department of Electrical Engineering,I.I.T.Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K.Radhakrishna Rao , Department of Electrical Engineering,I.I.T.Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K.Radhakrishna Rao , Department of Electrical Engineering,I.I.T.Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K.Radhakrishna Rao , Department of Electrical Engineering,I.I.T.Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K.Radhakrishna Rao , Department of Electrical Engineering,I.I.T.Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K.Radhakrishna Rao , Department of Electrical Engineering,I.I.T.Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K.Radhakrishna Rao , Department of Electrical Engineering,I.I.T.Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K.Radhakrishna Rao , Department of Electrical Engineering,I.I.T.Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K.Radhakrishna Rao , Department of Electrical Engineering,I.I.T.Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K.Radhakrishna Rao , Department of Electrical Engineering,I.I.T.Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K.Radhakrishna Rao , Department of Electrical Engineering,I.I.T.Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K.Radhakrishna Rao , Department of Electrical Engineering,I.I.T.Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K.Radhakrishna Rao , Department of Electrical Engineering,I.I.T.Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K.Radhakrishna Rao , Department of Electrical Engineering,I.I.T.Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Analog ICs by Prof. K.Radhakrishna Rao , Department of Electrical Engineering,I.I.T.Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

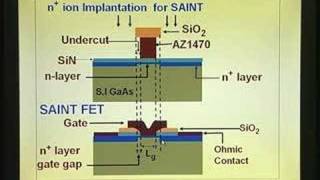

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in.GaAs MESFET Characteristics and Equivalent Circuit

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in.Dynamic CMOS ;Transmission Gates;Realization Of MUX,Decoder,D-F/F

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in.Heterojunction Bipolar Transistor Based ECL; ECL Gate Array

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in.Polyemitter Bipolar Transistor In ECL; Propagation Delay

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in.Emitter Function Logic;Low Power ECL;Current Mirror Control Logic.

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta , Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta , Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta , Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta , Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in. Lecture Title: Stacked I-square L ; I- square L - TTL Interfacing

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta , Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in. Lecture Title: Schottky Transistor Logic; Heterojunction I-square L.

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta , Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta , Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in. I-square L - Condition for Proper Operation; Noise margin

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta , Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in. Lecture Title: Edge triggered D-F/F and Decoder realization Using I-square L

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta , Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr. Amitava Dasgupta , Department of Electrical Engineering, IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr . Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr . Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr . Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr . Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr . Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in. Lecture Title:Schottky Transistor Introduction to Bipolar Logic Circuits

Lecture Series on Digital Integrated Circuits by Dr . Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr . Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr . Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr . Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Digital Integrated Circuits by Dr . Amitava Dasgupta, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Lecture series on Electro Magnetic Field, by Prof. Harishankar Ramachandran, Dept of Electrical Engineering, IIT Madras

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Lecture series on Electro Magnetic Field, by Prof. Harishankar Ramachandran, Dept of Electrical Engineering, IIT Madras

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

Electro Magnetic Field

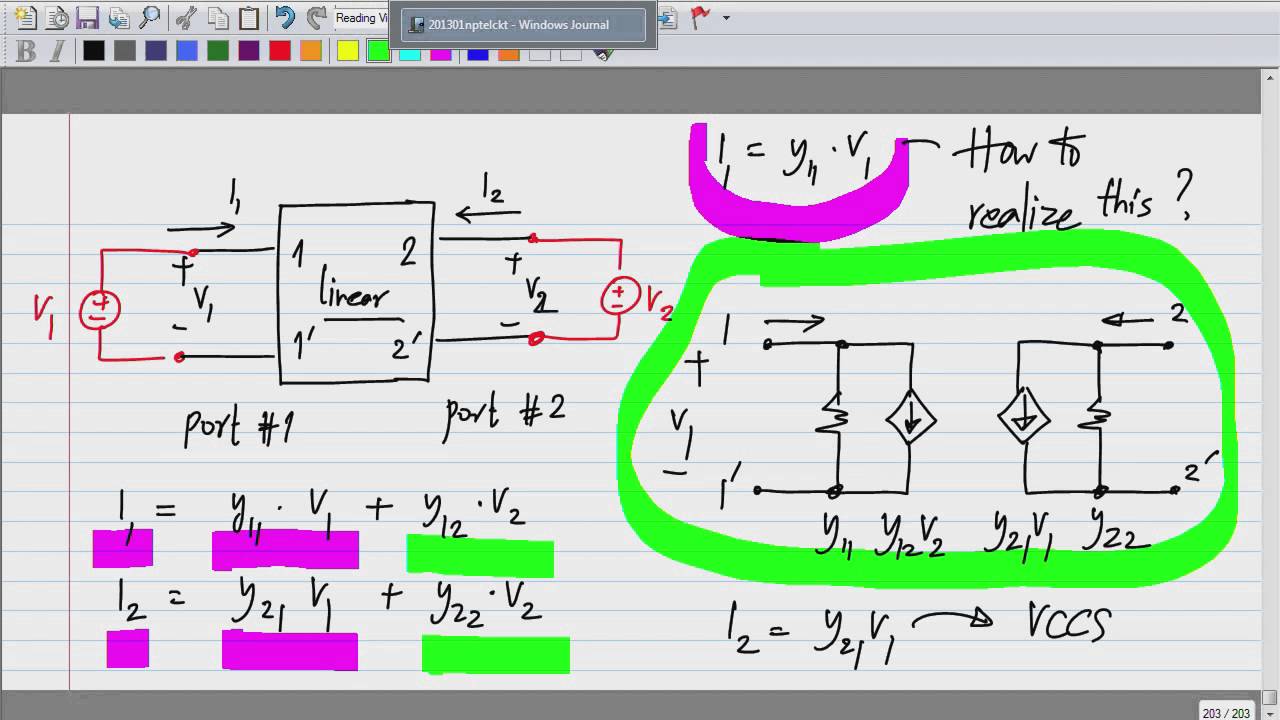

Lecture Series on Networks and Systems by Prof.V.G.K.Murti, Department of Electrical Engineering, IIT Madras. For More details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof.V.G.K.Murti, Department of Electrical Engineering, IIT Madras. For More details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof.V.G.K.Murti, Department of Electrical Engineering, IIT Madras. For More details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof.V.G.K.Murti, Department of Electrical Engineering, IIT Madras. For More details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof.V.G.K.Murti, Department of Electrical Engineering, IIT Madras. For More details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof.V.G.K.Murti, Department of Electrical Engineering, IIT Madras. For More details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof.V.G.K.Murti, Department of Electrical Engineering, IIT Madras. For More details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof.V.G.K.Murti, Department of Electrical Engineering, IIT Madras. For More details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof.V.G.K.Murti, Department of Electrical Engineering, IIT Madras. For More details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof.V.G.K.Murti, Department of Electrical Engineering, IIT Madras. For More details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof.V.G.K.Murti, Department of Electrical Engineering, IIT Madras. For More details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof.V.G.K.Murti, Department of Electrical Engineering, IIT Madras. For More details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof.V.G.K.Murti, Department of Electrical Engineering, IIT Madras. For More details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof.V.G.K.Murti, Department of Electrical Engineering, IIT Madras. For More details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof.V.G.K.Murti, Department of Electrical Engineering, IIT Madras. For More details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof.V.G.K.Murti, Department of Electrical Engineering, IIT Madras. For More details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof.V.G.K.Murti, Department of Electrical Engineering, IIT Madras. For More details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof.V.G.K.Murti, Department of Electrical Engineering, IIT Madras. For More details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof.V.G.K.Murti, Department of Electrical Engineering, IIT Madras. For More details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof.V.G.K.Murti, Department of Electrical Engineering, IIT Madras. For More details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

Lecture Series on Networks and Systems by Prof. V.G.K.Murti, Department of Electrical Engineering,IIT Madras. For more details on NPTEL visit http://nptel.iitm.ac.in

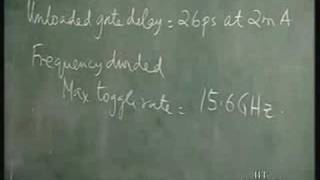

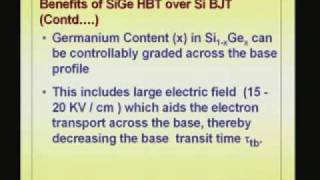

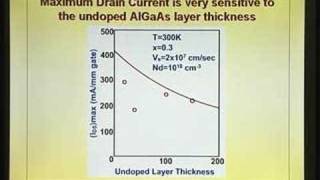

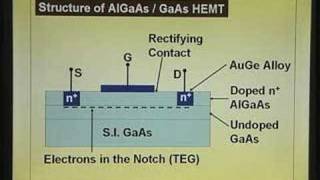

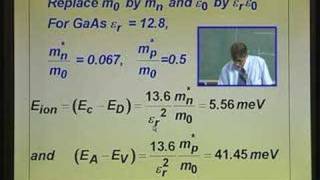

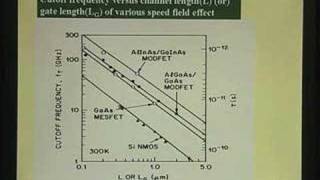

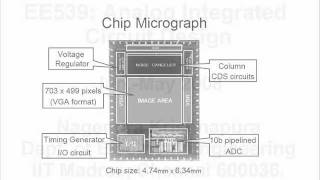

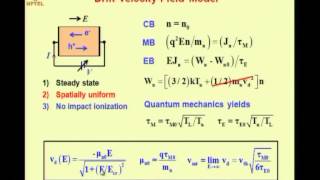

High Speed Devices&Circuits

High Speed Devices&Circuits

High Speed Devices&Circuits

High Speed Devices&Circuits

High Speed Devices&Circuits

High Speed Devices&Circuits

High Speed Devices&Circuits

High Speed Devices&Circuits

High Speed Devices&Circuits